In today's data-driven world, applications requiring massive computational power – such as artificial intelligence training, 3D rendering, and scientific simulations – demand memory solutions that go beyond standard consumer-grade components. This article explores specialized memory modules engineered to handle extreme workloads while maintaining stability and efficiency.

One critical player in this space is DDR5 RAM with on-die ECC (Error-Correcting Code). Unlike traditional ECC memory that requires additional modules, this technology integrates error correction directly into each memory chip. Samsung’s DDR5-6400 ODE series, for instance, achieves 51.2 GB/s bandwidth while automatically detecting and fixing single-bit errors – a vital feature for servers processing terabytes of genomic data or financial transaction records.

For GPU-accelerated computing, High Bandwidth Memory (HBM) has become the gold standard. The HBM3 specification pushes this further with 819 GB/s per stack through advanced packaging techniques like microbump connections. Consider AMD’s Instinct MI300 accelerators: By vertically stacking eight 16GB DRAM dies connected via 1024-bit interfaces, they achieve 5.3 TB/s aggregate bandwidth – crucial for training neural networks with billions of parameters.

Enterprise environments often deploy Load-Reduced DIMMs (LRDIMMs) to overcome signal integrity challenges in dense configurations. Kingston’s 256GB LR-DDR4 module uses a specialized buffer chip to minimize electrical load, enabling data centers to deploy 8TB per server node. This proves indispensable for in-memory databases like SAP HANA, where query speeds directly correlate with accessible memory capacity.

Emerging non-volatile solutions also warrant attention. Intel’s Optane Persistent Memory 300 series blurs the line between storage and memory, offering up to 512GB per module with byte-addressable persistence. During power failures in real-time analytics systems, this technology preserves in-progress calculations – a feature demonstrated in CERN’s particle collision simulations where unexpected shutdowns previously caused weeks of recomputation.

Developers working with these modules should note specific optimization requirements. For example, when using HBM2e in FPGA-based systems, modifying memory controller settings through Vivado’s XSDB console often becomes necessary:

create_hbm_config -hbm_ip hbm_0 -cfg_file hbm_config.cfg

set_property INTERFACE {AXI_MASTER} [get_hbm_configs hbm_config]

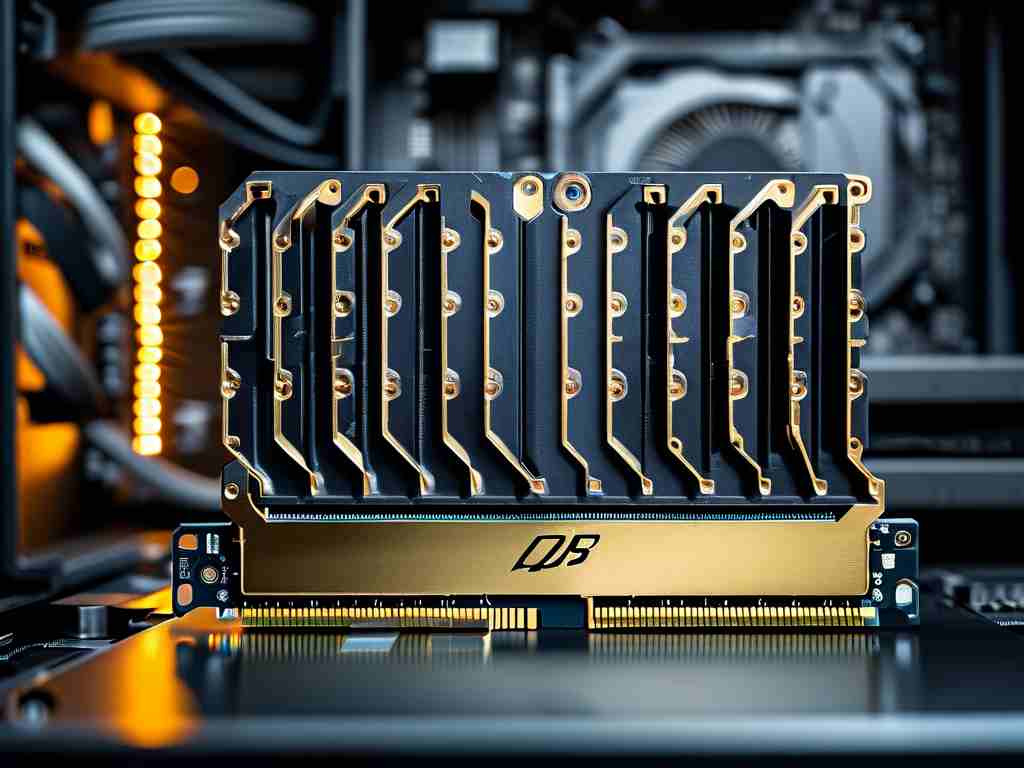

Thermal management presents another challenge. Crucial’s Ballistix MAX DDR4-5100 employs aluminum heat spreaders with graphene coating, reducing operating temperatures by 12°C compared to standard designs under sustained AVX-512 vector processing loads.

Looking ahead, technologies like Compute Express Link (CXL) promise to revolutionize memory scalability. Micron’s prototype CXL 2.0-attached memory expansion cards allow servers to dynamically allocate up to 4PB of pooled memory – a potential game-changer for cloud-based molecular dynamics simulations requiring unpredictable memory bursts.

When selecting memory for intensive workloads, professionals should evaluate:

- Sustained bandwidth under full load (not just peak specs)

- Compatibility with specific CPU memory controllers

- Power efficiency per gigabyte transferred

- Vendor firmware update support cycles

As computational demands continue escalating, memory innovation remains pivotal in preventing processing bottlenecks across industries – from weather modeling to cryptocurrency mining operations.